# Technical Reference Manual USAR ACPITroller™ 342

System Management Family

## **UR8HC342**

HID & ACPI Embedded Controller

## Confidential

Preliminary

Document Number: DOC8-342-TR-080 Date: September 2000 © 1999-2000 USAR – A Semtech Company

#### **USAR – A Semtech Company**

#### INTELLECTUAL PROPERTY DISCLAIMER

This specification is provided "as is" with no warranties whatsoever including any warranty of merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification or sample.

A license is hereby granted to reproduce and distribute this specification for internal use only. No other license, expressed or implied to any other intellectual property rights is granted or intended hereby. Authors of this specification disclaim any liability, including liability for infringement of proprietary rights, relating to the implementation of information in this specification. Authors of this specification also do not warrant or represent that such implementation(s) will not infringe such rights.

All other product names are trademarks, registered trademarks, or servicemarks of their respective owners.

## **Table of contents**

#### **Chapter 1 / Introduction**

| Document revisions                     | 1-1  |

|----------------------------------------|------|

| Overview                               | 1-3  |

| Scope of this document                 | 1-4  |

| Features at a glance                   | 1-5  |

| Pin overview                           | 1-6  |

| Pin usage                              | 1-7  |

| Pin description                        | 1-8  |

| USAR ACPITroller™ sample configuration | 1-11 |

#### Chapter 2 / Human input device controller interface

| HIDC bus interface               | 2-1  |

|----------------------------------|------|

| USAR ACPITroller™ HIDC registers | 2-2  |

| HIDC commands                    | 2-5  |

| PS/2 information registers       | 2-12 |

#### Chapter 3 / AlphaKey™ keyboard manager

| Overview                                         | 3-1 |

|--------------------------------------------------|-----|

| USAR AlphaKey™ features at a glance              | 3-3 |

| USAR AlphaKey™ hardware configuration            | 3-3 |

| PS/2 keyboard protocol command and data handling | 3-6 |

| USAR AlphaKey™ keyboard matrix                   | 3-8 |

| USAR AlphaKey™ key numbers                       | 3-9 |

#### Chapter 4 / AlphaMouse™ pointing devices manager

| Overview                                  | 4-1 |

|-------------------------------------------|-----|

| Multiplex mode                            | 4-2 |

| Legacy mode                               | 4-3 |

| Chapter 5 / Embedded controller interface |     |

| UR8HC342 EC bus interface                 | 5-1 |

| UR8HC342 embedded controller registers    | 5-2 |

| Port Operation                            | 5-4 |

| EC Commands                               | 5-6 |

#### Chapter 6 / SCI & SWI interrupt generation

| Event interrupts     | 6-1 |

|----------------------|-----|

| Interrupt generation | 6-4 |

#### Chapter 7 / SMBus host controller interface

| Overview                                  | 7-1 |

|-------------------------------------------|-----|

| SMBus overview                            | 7-1 |

| The SMBus host controller interface       | 7-1 |

| SMBus alarm message & SMBus alert process | 7-2 |

| SMBus error recovery                      | 7-3 |

| SMBus host register space                 | 7-3 |

| SMBus host registers                      | 7-3 |

| Chapter 8 / General input/output options  |     |

| Internal virtual SMBus device             | 8-1 |

Table of contents

| GIO0: LED driver                            |                                | _ |

|---------------------------------------------|--------------------------------|---|

| GIO1: Analog output fo                      | or flat panel digital controls |   |

| GIO2: 3-channel 10-bi                       | t analog to digital converter  |   |

| GIO3: general purpose                       | e I/O                          |   |

|                                             |                                |   |

| Chapter 9 / Electri                         | cal characteristics            |   |

| Chapter 9 / Electri<br>Absolute maximum rat |                                |   |

| Absolute maximum rat                        |                                |   |

#### Appendix A

| USAR AlphaKey™ standard PS/2 key number definitions | A-1 |

|-----------------------------------------------------|-----|

| Appendix B                                          |     |

| USAR AlphaKey™ default keyboard matrix and layout   | B-1 |

| Appendix C                                          |     |

| Standard SMBus registers                            | C-1 |

|                                                     |     |

This page intentionally left blank

ACPITroller<sup>™</sup> Basic UR8HC342 **Preliminary** system management controller product

## Introduction

## Document revisions

#### **Document revision history**

| Date       | Version | Comments                                                                                                 |

|------------|---------|----------------------------------------------------------------------------------------------------------|

| 1999/07/28 | 0.60    | Initial draft                                                                                            |

| 1999/09/14 | 0.70    | Incorporated technical corrections and clarifications; grayed out features that are still in development |

| 2000/09/11 | 0.80    | Incorporated technical corrections and clarifications                                                    |

ACPITroller™ Basic UR8HC342 **Preliminary** system management controller product

This page intentionally left blank

ACPITroller<sup>™</sup> Basic UR8HC342 **Preliminary** system management controller product

## **USAR ACPIT**roller<sup>™</sup> technical reference introduction

### Overview

The UR8HC342 is a single IC that functions both as an 8042-type Human Input Device Controller (HIDC) and an ACPI-compliant Embedded Controller (EC). The UR8HC342 provides the typical functionality of an 8042-type HID Controller with embedded key and motion scanning. In addition, the UR8HC342 functions as an ACPI compliant Embedded Controller (EC) and SMBus host.

The IC achieves unparalleled minimum power consumption (typically less than 1µA) due to USAR's patented Zero-Power<sup>TM</sup> technologies for both PS/2 ports and the SMBus port – an industry first. The USAR ACPITroller<sup>TM</sup> can power down even when devices are connected and active. Based on USAR's patented Zero-Power<sup>TM</sup> technology, the UR8HC342 always operates in the "STOP" mode, independently of the configuration and without any data or event losses.

The USAR AlphaKey<sup>™</sup> keyboard manager, implemented in the UR8HC342, provides OEMs with the most advanced and versatile keyboard management functions, including keyboard matrix programming.

The USAR AlphaMouse<sup>™</sup> pointing device manager supports MouseWheel operation, recommended by Microsoft, for both the embedded and the hotplugged external pointing devices.

Using the UR8HC342, system designers can implement systems that take advantage of the SMBus, the Smart Battery System, and the ACPI specifications, all using a single IC. The UR8HC342 uses USAR's patented Zero-Power™ SMBus technology and is the lowest power consumption IC in the market today. The UR8HC342 can be customized easily through an extensive library of hardware and firmware modules in order to accommodate specialized configurations at low production cost.

#### **SMBus Host**

The IC manages one hardware SMBus port. The IC complies with version 1.0 of the Smart Battery System (SBS) and SMBus specifications.

## Scope of this document

This is a preliminary document. Although all the functions described in this document have been tested in USAR's laboratories, the document may contain errors and inaccuracies. Prior to committing to design, consult with USAR for up to date revisions. Some features described in this document are still in development; these features are identified by grayed-out text.

USAR has used every effort to design the part in the best manner to serve the current industry needs. Nevertheless, input from OEMs for both function and configuration is appreciated and may result in future modifications and enhancements.

This document is still in a confidential state, as printed on the bottom of each page, and it cannot be distributed without explicit permission from USAR.

Please forward all your comments or questions regarding this product and document to:

acpi@usar.com

USAR Systems, Inc. 568 Broadway New York, NY 10012 212.226.2042 Telephone 212.226.3215 Telefax

#### **Evaluation kits**

For information or to order a USAR ACPITroller<sup>™</sup> evaluation kit, send your email to:

info@usar.com

ACPITroller<sup>™</sup> Basic UR8HC342 **Preliminary** system management controller

system management controller product

## Features at a glance

- Typical power consumption of less than 1µA as a result of USAR's patented Zero-Power™ technologies; the IC can power down even when devices are connected and active

- Patented Zero-Power<sup>™</sup> operation of all PS/2 ports and the SMBus port an industry first

- AlphaMouse<sup>™</sup> pointing device manager supports hot-plugging and hotswapping of standard two-button and three-button mice without a special driver; it also supports hot-plugging and hot-swapping of MouseWheel mice with a MouseWheel-capable driver

- Two external PS/2 ports for external keyboard and mouse with auto-detect and hot-plug support

- Simultaneous operation of external and internal input devices

- Support of MouseWheel functionality for both embedded and external pointing devices, even with hot-plug connections, with a MouseWheel-capable driver

- 8042-compatible host interface and functionality

- •8 x 16 fully programmable scanned keyboard matrix

- Support of all three keyboard scan code sets

- ACPI EC host interface

- Support of up to 6 ACPI GPE interrupt inputs

- ACPI Power Button and Power Button Override support

- SMBus compatible host complies with version 1.0 of the SBS/SMBus specifications

- Blocks potentially dangerous Smart Battery System commands (write charger voltage and write charger current) issuing from the host system

- Up to three 10-bit A/D inputs

- Two D/A and two PWM outputs

- Easily customized for specialized applications

- Three-volt and five-volt operation

- AlphaMouse<sup>™</sup> performs active PS/2 multiplexing of input from different types of mice simultaneously, with the appropriate driver(s)

- Support of the USAR ScreenCoder™ PS/2 absolute and relative touchscreen encoder, with the appropriate driver

- Support of the five-button mouse, with an appropriate driver

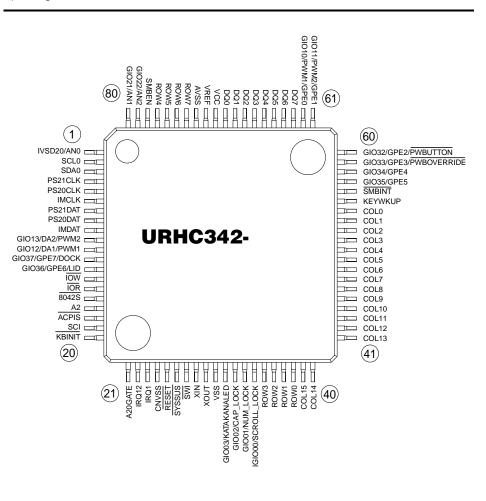

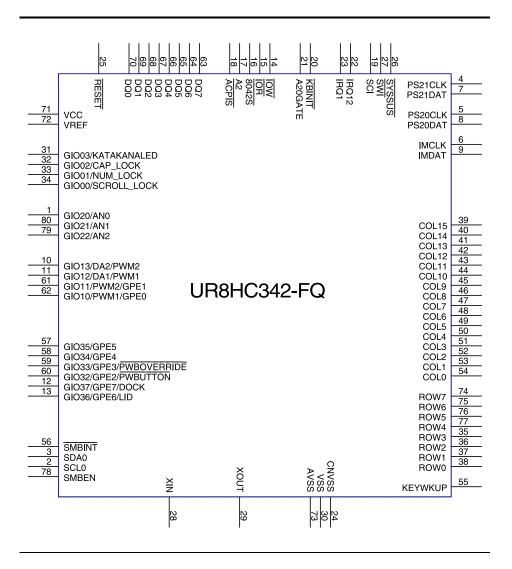

## Pin overview

The figure below illustrates the pins for the UR8HC342 implementation for the FQ package.

system management controller product

## Pin usage

## Pin description

The following table describes the pins of the USAR UR8HC342 ACPITroller™.

Note: If a pin is active low, then there is an overscore over the pin name in schematics, and there is a single underscore character (\_) preceding the pin name in tables and text; for example, \_RESET.

#### **ACPIT**roller<sup>™</sup> pin descriptions

| Pin Name         | Pin      | Description                                       |

|------------------|----------|---------------------------------------------------|

|                  | no.      |                                                   |

| Power Supply     |          |                                                   |

| AVSS             | 73       | Analog signal ground                              |

| CNVSS            | 24       | Should be tied to ground                          |

| VCC              | 71       | Vcc 3-5 volts                                     |

| VREF             | 72       | Analog circuitry reference voltage                |

| VSS              | 30       | Ground                                            |

| Oscillator pins  |          |                                                   |

| XIN              | 28       | Oscillator input (8 MHz operating frequency)      |

| XOUT             | 29       | Oscillator output                                 |

| Reset            |          |                                                   |

| _RESET           | 25       | Controller hardware reset pin                     |

| System bus inter | face pin | IS                                                |

| _8042S           | 16       | 8042 keyboard controller port select signal input |

| _ACPIS           | 18       | ACPI embedded controller port select signal input |

| _IOR             | 15       | X-bus/ISA I/O read signal input                   |

| _IOW             | 14       | X-bus/ISA I/O write signal input                  |

| IRQ1             | 23       | Keyboard interrupt output                         |

| IRQ12            | 22       | Mouse interrupt output                            |

| _KBINIT          | 20       | Keyboard initialize output                        |

| A2               | 17       | X-bus/ISA address 2 input                         |

| A20GATE          | 21       | A20 Gate output signal                            |

| DQ0              | 70       | X-bus/ISA parallel data I/O ports                 |

| DQ1              | 69       |                                                   |

| DQ2              | 68       |                                                   |

| DQ3              | 67       |                                                   |

| DQ4              | 66       |                                                   |

| DQ5              | 65       |                                                   |

| DQ6              | 64       |                                                   |

| DQ7              | 63       |                                                   |

ACPITroller™ Basic UR8HC342 **Preliminary**

system management controller product

#### **ACPITroller™ pin descriptions**

| Pin Name                    | Pin<br>no. | Description                                                                                                                                                |

|-----------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACPI, SMBus, and g          | enera      | I purpose I/O signals                                                                                                                                      |

| SCI                         | 19         | System control interrupt output                                                                                                                            |

| _SMBINT                     | 56         | SMBus interrupt input                                                                                                                                      |

| _SWI                        | 27         | System wake-up event interrupt output                                                                                                                      |

| _SYSSUS                     | 26         | System suspend input                                                                                                                                       |

| GIO00<br>/SCROLL_LOCK       | 34         | This pin can be programmed to act as a keyboard LED or as a GPIO pin.                                                                                      |

| GIO01/NUM_LOCK              | 33         | This pin can be programmed to act as a keyboard LED or as a GPIO pin.                                                                                      |

| GIO02/CAP_LOCK              | 32         | This pin can be programmed to act as a keyboard LED or as a GPIO pin.                                                                                      |

| GIO03<br>/KATAKANALED       | 31         | This pin can be programmed to act as a keyboard LED or as a GPIO pin.                                                                                      |

| GIO10/PWM1/GPE0             | 62         | GIO1 bit 0 or PWM output or ACPI GPE                                                                                                                       |

| GIO11/PWM2/GPE1             | 61         | GIO1 bit 1 or PWM output or ACPI GPE                                                                                                                       |

| GIO12/DA1/PWM1              | 11         | This pin can be configured as GPIO, as D/A output, or PWM output.                                                                                          |

| GIO13/DA2/PWM2              | 10         | This pin can be configured as GPIO, as D/A output, or PWM output.                                                                                          |

| GIO20/AN0                   | 1          | This pin can be configured as a 10-bit A/D input or logic I/O.                                                                                             |

| GIO21/AN1                   | 80         | This pin can be configured as a 10-bit A/D input or logic I/O.                                                                                             |

| GIO22/AN2                   | 79         | GIO2 bit or A/D input                                                                                                                                      |

| GIO36/GPE6/LID              | 13         | GIO3 bit 0 or ACPI general purpose event (GPE); capable of detecting both negative and positive signal transitions; typically serves the LID ACPI function |

| GIO37/GPE7/DOCK             | 12         | GIO3 bit 1 or ACPI GPE; capable of detecting both negative and positive signal transitions; typically serves the DOCK ACPI function                        |

| GIO32/GPE2<br>/_PWBUTTON    | 60         | GIO3 bit 2 or ACPI GPE; typically an ACPI "Power Button" input.                                                                                            |

| GIO33/GPE3<br>/_PWBOVERRIDE | 59         | GIO3 bit 3 or ACPI GPE; typically an ACPI "Power Button<br>Override" input                                                                                 |

| GIO34/GPE4                  | 58         | GIO3 bit 4 or ACPI GPE 4                                                                                                                                   |

| GIO35/GPE5                  | 57         | GIO3 bit 5 or ACPI GPE 5                                                                                                                                   |

| SCL0                        | 2          | This pin acts as the clock line for the SMBus                                                                                                              |

| SDA0                        | 3          | This pin acts as the data line for the SMBus                                                                                                               |

#### **ACPITroller™ pin descriptions**

| Pin Name       | Pin<br>no. | Description                                                                                                                                                                                                                                                  |

|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACPI, SMBus, a | nd genera  | Il purpose I/O signals                                                                                                                                                                                                                                       |

| SMBEN          | 78         | This output pin allows the SMBus latch to notify the ACPITroller <sup>™</sup> when SMBus activity has been detected. It is used to wake the ACPITroller <sup>™</sup> from sleep mode, and to disable all PS/2 inputs while SMBus processing is taking place. |

| Scanned matrix | c pins     |                                                                                                                                                                                                                                                              |

| COLO           | 54         | Column matrix outputs                                                                                                                                                                                                                                        |

| COL1           | 53         |                                                                                                                                                                                                                                                              |

| COL2           | 52         |                                                                                                                                                                                                                                                              |

| COL3           | 51         |                                                                                                                                                                                                                                                              |

| COL4           | 50         |                                                                                                                                                                                                                                                              |

| COL5           | 49         |                                                                                                                                                                                                                                                              |

| COL6           | 48         |                                                                                                                                                                                                                                                              |

| COL7           | 47         |                                                                                                                                                                                                                                                              |

| COL8           | 46         |                                                                                                                                                                                                                                                              |

| COL9           | 45         |                                                                                                                                                                                                                                                              |

| COL10          | 44         |                                                                                                                                                                                                                                                              |

| COL11          | 43         |                                                                                                                                                                                                                                                              |

| COL12          | 42         |                                                                                                                                                                                                                                                              |

| COL13          | 41         |                                                                                                                                                                                                                                                              |

| COL14          | 40         |                                                                                                                                                                                                                                                              |

| COL15          | 39         |                                                                                                                                                                                                                                                              |

| KEYWKUP        | 55         | Key wake-up output                                                                                                                                                                                                                                           |

| ROW0           | 38         | Row matrix inputs                                                                                                                                                                                                                                            |

| ROW1           | 37         |                                                                                                                                                                                                                                                              |

| ROW2           | 36         |                                                                                                                                                                                                                                                              |

| ROW3           | 35         |                                                                                                                                                                                                                                                              |

| ROW4           | 77         |                                                                                                                                                                                                                                                              |

| ROW5           | 76         |                                                                                                                                                                                                                                                              |

| ROW6           | 75<br>74   |                                                                                                                                                                                                                                                              |

| ROW7           | /4         |                                                                                                                                                                                                                                                              |

| PS/2 ports     |            |                                                                                                                                                                                                                                                              |

| IMCLK          | 6          | PS/2 clock line for internal mouse                                                                                                                                                                                                                           |

| IMDAT          | 9          | PS/2 data line for internal mouse                                                                                                                                                                                                                            |

| PS20CLK        | 5          | Clock line for external PS/2 port 0; both external PS/2 ports                                                                                                                                                                                                |

|                |            | support hot-plug ins and auto-select for keyboard or mouse                                                                                                                                                                                                   |

| PS20DAT        | 8          | Data line for external PS/2 port 0                                                                                                                                                                                                                           |

| PS21CLK        | 4          | Clock line for external PS/2 port 1                                                                                                                                                                                                                          |

| PS21DAT        | 7          | Data line for external PS/2 port 1                                                                                                                                                                                                                           |

|                |            | en en la la c                                                                                                                                                                                                                                                |

ACPITroller<sup>™</sup> Basic UR8HC342 **Preliminary** system management controller product

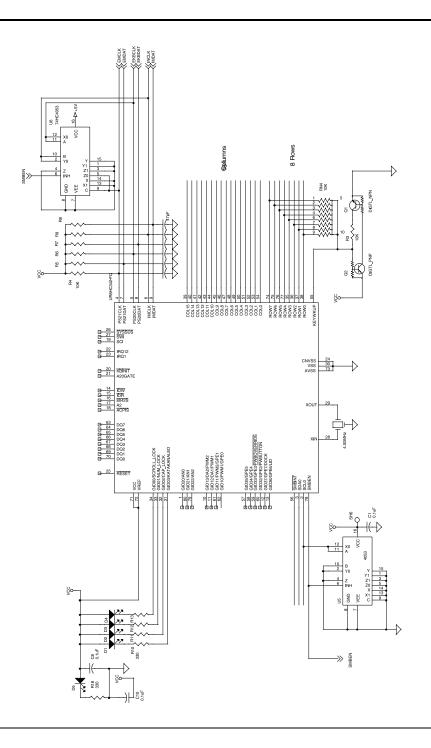

## USAR ACPITroller<sup>™</sup> sample configuration

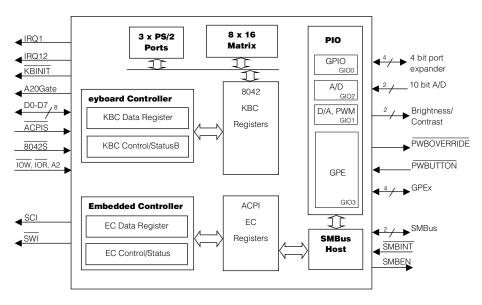

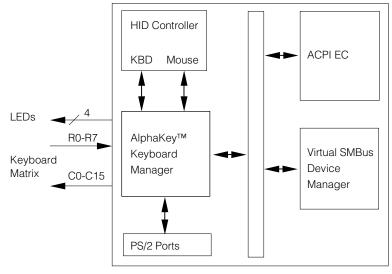

The USAR ACPITroller<sup>™</sup> is a highly versatile part that can be configured to accommodate different OEM configurations. The block diagram below illustrates the major functional components of the USAR ACPITroller<sup>™</sup> in a simple configuration.

#### **USAR ACPITroller™ sample configuration**

Simple configuration block diagram of UR8HC342

In the configuration shown above the USAR ACPITroller<sup>™</sup> is configured to provide besides the basic EC and KC functionality the following:

- Power button and power button override function implemented on GPE pins

- 4 general-purpose I/O pins

- 4 additional GPE inputs

- 3 pins that can be configured as 10 bit A/D channels or GPIO

- 2 pins that can be configured as D/A or PWM outputs or GPIO

- One Zero-Power™ SMBus port

### USAR – A Semtech Company Introduction

ACPITroller™ Basic UR8HC342 **Preliminary** system management controller product

This page intentionally left blank

## **USAR ACPIT**roller<sup>™</sup> human input device controller (HIDC) interface

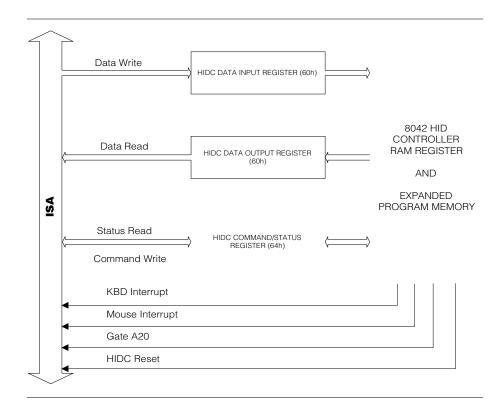

## HIDC bus interface

The Human Input Device Controller (HIDC) portion of the USAR ACPITroller<sup>™</sup> interfaces to the host ISA bus via two I/O addresses, generally 0x60 and 0x64. The following diagram illustrates the HIDC register architecture.

USAR ACPITroller™ HID Controller Interface

## USAR ACPITroller™ HIDC registers

The HIDC portion of the USAR ACPITroller<sup>™</sup> contains three registers that occupy two I/O locations. The registers are listed in the following table:

#### **HIDC** registers

| Name       | Description | I/O function | I/O Port |  |

|------------|-------------|--------------|----------|--|

|            |             |              | Address  |  |

| HIDC_SC(W) | Command     | IOW          | 0x64     |  |

| HIDC_SC(R) | Status      | IOR          | 0x64     |  |

| HIDC_DATA  | Data        | IOR/IOW      | 0x60     |  |

#### HIDC Status Register, HIDC\_SC (R)

The HIDC Status Register is a read-only register that indicates the current status of the Keyboard Controller interface. It contains the following fields:

| HIDC_SC (R) status register bit definitions |          |           |          |  |  |

|---------------------------------------------|----------|-----------|----------|--|--|

| bit7                                        | bit6     | bit5      | bit4     |  |  |

| HIDC_PE                                     | HIDC_GTO | HIDC_AOBF | HIDC_INH |  |  |

| bit3                                        | bit2     | bit1      | bit0     |  |  |

| HIDC_CMD                                    | HIDC_SF  | HIDC_IBF  | HIDC_OBF |  |  |

#### **HIDC\_SC (R)** status register bit descriptions

| HIDC_PE   | Parity Error<br>1 – Indicates a parity error. In this case 0xFF is placed in the data register<br>0 – Indicates that the last byte of data received from the PS/2 device had odd<br>parity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIDC_GTO  | General Time-Out<br>1 – Indicates that a time-out occurred during a transaction with one of the PS/2<br>devices. The HIDC_GTO is set in any of the following situations:<br>– Reception of a byte from a PS/2 device started but did not complete within<br>the Receive Time Out limit. The HIDC places 0xFF into the data register<br>– A transmission started by the HIDC to a PS/2 device, but was not completed<br>within the Transmit Time Out limit. The HIDC places 0xFE into the data register<br>– A transmission started by the HIDC places 0xFE into the data register<br>– A byte requiring response (command) was clocked out to a PS/2 device but<br>it was not acknowledged within the ACK Time Limit<br>– A command byte was clocked out and a response was received with a parity<br>error. In this case both HIDC_GTO and HIDC_PE are set<br>0 – No Time-Out |

| HIDC_AOBF | Auxiliary Output Buffer Full<br>This bit works in conjunction with HIDC_OBF (Output Buffer Full) bit<br>1 – When HIDC_OBF is also set, indicates that data from the Auxiliary device is<br>pending in the data register<br>0 – When HIDC_OBF is set, indicates that Keyboard data or a HIDC response<br>is pending in the data register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| HIDC_INH  | Inhibit Switch<br>1 – Keyboard is enabled<br>0 – Password state is active and the keyboard is inhibited<br>(For more information, see section below on Password Protection)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HIDC_CMD  | Command/Data<br>1 – Data register contains a command byte (set by the host, read by the HIDC)<br>0 – Data register contains a data byte (set by the host, read by the HIDC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HIDC_SF   | System Flag<br>1 – The System Flag bit in the Controller Command byte is set to one<br>0 – The System Flag bit in the Controller Command byte is set to zero (default<br>after reset)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HIDC_IBF  | Input Buffer Full<br>1 – Input buffer is full (data has been written in the data register but has not<br>been read by the HIDC)<br>0 – Input buffer is empty (data has been read by the HIDC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HIDC_OBF  | Output Buffer Full<br>1 – Data ready for host in the Data Register (generate appropriate interrupt)<br>0 – Data has been read by the host (set automatically after an IO read<br>operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Command register, HIDC\_SC (W)

The HIDC\_SC (W) command register is a write-only register that allows commands to be issued to the keyboard controller. Write operations to this port are latched into the input data register; the input buffer full (HIDC\_IBF) flag is set in the status register. Writes to this location also cause the HIDC\_CMD (Command/Data) bit to be set in the status register. This

enables the keyboard controller to differentiate the start of a command sequence from a data byte write operation.

#### Data Register, HIDC\_DATA(R/W)

The HIDC\_DATA(R/W) data register is a read/write register that allows command/data bytes to be issued to the keyboard controller while also enabling the host system to read data returned by the keyboard controller. Writes to this port are latched into the input data register; the input buffer full (HIDC\_IBF) flag is set in the status register. Data written by the system into this register is generally transmitted to the appropriate PS/2 device, unless the HIDC expects a data byte as part of a command sequence. Reads from this register return data from the output data register and clear the output buffer full (HIDC\_OBF) flag in the status register.

## **HIDC** Commands

Any byte written by the host system into the HIDC\_SC register is interpreted as a command. The USAR ACPITroller<sup>™</sup> supports all the standard 8042 commands, as well as expanded commands, as described below.

#### **Standard 8042 commands**

| Hex Value | Description                                                                                                                                                                                                                                 |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 20        | Read Controller Command byte                                                                                                                                                                                                                |  |  |  |

| 21-3F     | Read HIDC RAM Registers. Address is specified by bit0-bit5                                                                                                                                                                                  |  |  |  |

| 60        | Write Controller Command byte. The following byte is data                                                                                                                                                                                   |  |  |  |

| 61-7F     | Write HIDC RAM Registers. Address is specified by bit0-bit5, and the following byte is data                                                                                                                                                 |  |  |  |

| A4        | Test Password Installed. The result is placed in the data buffer as follows:<br>– 0xFA – installed<br>– 0xF1 – not installed<br>(See below)                                                                                                 |  |  |  |

| A5        | Load Password. Data follows until a null (0) is detected (See below)                                                                                                                                                                        |  |  |  |

| A6        | Enable Password. This command is valid only when a password is loaded in the controller (See below)                                                                                                                                         |  |  |  |

| A7        | Disable Auxiliary Device Interface. This command sets bit 5 of the Controller<br>Command byte and disables the Auxiliary Device clock line                                                                                                  |  |  |  |

| A8        | Enable Auxiliary Device Interface. This command clears bit 5 of the Controller Command byte and enables the Auxiliary Device clock line                                                                                                     |  |  |  |

| A9        | Auxiliary Device Interface Test. Test results are returned in the data buffer as<br>follows:<br>- 00 – No error<br>- 01 – Clock line stuck low<br>- 02 – Clock line stuck high<br>- 03 – Data line stuck low<br>- 04 – Data line stuck high |  |  |  |

| AA        | Controller self test, Return 55.                                                                                                                                                                                                            |  |  |  |

| AB        | Keyboard Device Interface Test. Test results are returned in the data buffer as<br>follows:<br>- 00 - No error<br>- 01 - Clock line stuck low<br>- 02 - Clock line stuck high<br>- 03 - Data line stuck high                                |  |  |  |

| AD        | Disable Keyboard Interface. This command sets bit 4 of the Controller Command byte and disables the Keyboard clock line                                                                                                                     |  |  |  |

| AE        | Enable Keyboard Interface. This command clears bit 4 of the Controller<br>Command byte and enables the Keyboard clock line                                                                                                                  |  |  |  |

| CO        | Read Input Port and place data in the data register                                                                                                                                                                                         |  |  |  |

| C2-C3     | Poll Input Port and update bit7-bit4 of the Status Register                                                                                                                                                                                 |  |  |  |

| D0        | Read Output Port and place data in the data register                                                                                                                                                                                        |  |  |  |

| D1        | Write Output Port. The next byte is written to the HIDC Output Port                                                                                                                                                                         |  |  |  |

| D2        | Write Keyboard Output Buffer. The next byte is played back as if originating from the keyboard                                                                                                                                              |  |  |  |

| D3        | Write Auxiliary Device Output Buffer. The next byte is played back as if originating from the Auxiliary Device                                                                                                                              |  |  |  |

#### **Standard 8042 commands**

| <b>Hex Value</b> | Description                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------|

| D4               | Write to Auxiliary Device. The next byte is transmitted to the Auxiliary Device                            |

| E0               | Read Test Inputs. Returns 0 (Type 1 controller)                                                            |

| F0-FF            | Pulse Output Port. This command pulses Output Port bits, defined by bit0-<br>bit3, for approximately 6 us. |

#### **Keyboard password**

The USAR ACPITroller<sup>™</sup> supports keyboard password functionality. There are three commands associated with the password operation.

- Load Password (0xA5)

- Test Password Installed (0xA4)

- Enable Password (0xA6)

The password can be loaded into the USAR ACPITroller<sup>™</sup> RAM area by the system at any time, using the "Load Password" command. The password can be up to seven bytes long and is loaded using Scan Code 1 (scan codes provided by the system).

The system can check if a password is installed using the "Test Password Installed" command. If a password is already installed, the system can enable the password by issuing the "Enable Password" command.

While the password is enabled, the HIDC enters the secure mode and behaves as follows:

- 1. The HIDC intercepts any incoming code stream from the keyboard and compares it with what is installed in the RAM password pattern. The HIDC discards any code from the keyboard and the auxiliary device that does not match the password. If an incoming code does not match either the next character in the pattern or the contents of RAM Register addresses 0x16 and 0x17, the HIDC resets its password pointer and the next incoming code is compared to the first byte of the password pattern.

- 2. While in secure mode, the HIDC does not pass any codes to the system or accept any commands.

- 3. After a match occurs, the HIDC resumes normal operation and starts passing codes to the host system.

There are four HIDC RAM Registers related to the password operation:

#### **Password associated RAM registers**

| RAM          | Address  | Description                                                                                                                                                  |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register     |          |                                                                                                                                                              |

| Security on  | 13H      | When the password is enabled, a non-zero value in this register forces the HIDC to output the contents of the register into the Data Register and issue IRQ1 |

| Security off | 14H      | When the password is matched, a non-zero value forces<br>the HIDC to output the register contents into the Data<br>Register and issue IRQ1                   |

| Make 1 & 2   | 16H, 17H | These registers can be loaded by the system with scan<br>codes that should be ignored during the password<br>match process (i.e., shift codes)               |

#### **HIDC RAM registers**

The HIDC has on-board RAM registers, listed in the table below. HIDC RAM Registers are accessed for read and write operations through the Read/Write HIDC RAM Register commands. A description of specific RAM registers follows.

#### **HIDC RAM registers**

| Description of Register                 |  |  |  |  |

|-----------------------------------------|--|--|--|--|

| Controller Command byte (Read or Write) |  |  |  |  |

| Not defined, system use                 |  |  |  |  |

| Security on                             |  |  |  |  |

| Security off                            |  |  |  |  |

| Make 1 and 2                            |  |  |  |  |

|                                         |  |  |  |  |

ACPITroller™ Basic UR8HC342 **Preliminary** system management controller product

#### **Controller command byte**

The Controller Command byte occupies address offset zero in the HIDC RAM Register space. The Controller Command byte can be accessed through general Read/Write or specific commands and contains the following bits:

#### **Controller command byte bit definitions**

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| RES  | TRS  | ADIS | KDIS | RES  | SF   | AIRQ | KIRQ |

#### **Controller command byte bits descriptions**

| RES  | Reserved                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRS  | Keyboard Translate<br>1 – Sets keyboard translation from Scan Code Set 2 to Scan Code Set 1<br>0 – Disables keyboard scan code translation           |

| ADIS | Disable Auxiliary Device<br>1 – HIDC disables the Auxiliary device by pulling the clock line low<br>0 – HIDC enables the Auxiliary device            |

| KDIS | Disable Keyboard<br>1 – HIDC disables the keyboard by pulling the clock line low<br>0 – HIDC enables the keyboard                                    |

| SF   | System Flag<br>The value written in this bit is placed in the relevant bit of the Status Register<br>(system use)                                    |

| AIRQ | Enable Auxiliary Device Interrupts<br>Setting this bit to 1 enables IRQ12 whenever an auxiliary device data byte is<br>placed into the data register |

| KIRQ | Enable Keyboard Interrupts<br>Setting this bit to 1 enables IRQ1 whenever a keyboard data byte is placed<br>into the data register                   |

#### Security on

The Security On register is used for Keyboard Password functionality. When the password is enabled, a non-zero value in this register forces the HIDC to output the contents of the register into the Data Register and issue IRQ1.

#### Security off

The Security Off register is used for Keyboard Password functionality. When the password is matched, a non-zero value forces the HIDC to output the register contents into the Data Register and issue IRQ1.

#### Make 1 and 2

These registers are used for Keyboard Password functionality and can be loaded by the system with scan codes that should be ignored during the password match process (i.e., shift codes).

#### AlphaKey<sup>™</sup> Control Register

This register controls local handling of the PS/2 keyboard protocol, defines pins as GPIO or keyboard LEDs, and enables and disables programming of the embedded keyboard matrix. Functional details are described in full in the AlphaKey™ Keyboard Manager chapter.

#### HIDC USAR expanded command set

In addition to the standard 8042 commands, the HIDC section implements a set of Expanded Commands, defined by USAR in order to accommodate the special functions implemented in the USAR ACPITroller<sup>™</sup> HID section. These commands provide BIOS, Drivers and application software with access to the following unique features of the USAR ACPITroller<sup>™</sup>:

- Version control

- OEM Programmable Area

- Scanned Keyboard Matrix programmability

#### **HIDC** expanded commands

| <b>Hex Value</b> | Description                                                             |

|------------------|-------------------------------------------------------------------------|

| B0               | Read model number, 1Byte                                                |

|                  | Bit7: – 0: Standard part                                                |

|                  | <ul> <li>– 1: Customized part</li> </ul>                                |

|                  | Bit6-Bit0: model number                                                 |

|                  | A value of 01H denotes the basic configuration                          |

| B1               | Read revision number, 1byte                                             |

| B2               | Write Program RAM Page Register                                         |

|                  | Valid Values: 0, 1                                                      |

| B3               | Read Program RAM Page Register, 1 byte                                  |

| B4               | Write Program RAM Pointer Register                                      |

|                  | Valid Values: 0 – FFh for page 0;                                       |

|                  | 0 – 7Fh for page 1;                                                     |

| B5               | Read Program RAM Pointer Register, 1 byte                               |

| B6               | Write to Program RAM in given page and current address                  |

| B7               | Read from Program RAM in given page and current address                 |

| B8               | Write data block to Program RAM, starting at specified address. This    |

|                  | command is followed by one byte block size, one byte address and data   |

| B9               | Read from Program RAM by specified address                              |

| BA               | Download Whole Matrix Layout0, follow by 128 bytes matrix               |

| BB               | Download Whole Num Lock and Fn Matrix Layout, follow by 96 bytes matrix |

| BC               | Download Whole Macro Function Pointer, follow by 16 bytes pointer       |

| BD               | Download Whole Macro Function Code, follow by 128 bytes code            |

For commands B6 and B7, the RAM pointer register automatically increments after each byte is read or written. The increment wraps from FFh to 00h within RAM Page 0 (you cannot implicitly write to Page 1), and from 7Fh to 00h within RAM Page 1.

For the download commands (BA, BB, BC, and BD), you must issue the command in the command/status register, than send each byte of data, one at a time, in the data register. You must verify that the input buffer full bit (bit 1 of the HIDC status register, as shown earlier in this chapter) has been cleared before sending the next byte. Each of these commands expects a

fixed number of data bytes. The HIDC must read all of the expected bytes before another command issues. If a new command issues before all expected bytes are read, the download command aborts and the rest of the matrix is unchanged.

## PS/2 information registers

Starting at offset 15 from the start of the 8042 extended register area, there are three read-only registers with information about the three PS/2 ports: registers R15-R17.

#### R15: 8042 configuration register 0 bit definitions (R)

| bit7 | bit 6 | bit 5         | bit 4  | bit 3  | bit 2 | bit 1 | bit 0 |

|------|-------|---------------|--------|--------|-------|-------|-------|

| MXEN | RES   | <b>M3PEND</b> | M2PEND | M1PEND | M3DIS | M2DIS | M1DIS |

#### R15: 8042 configuration register 0 bit descriptions (R)

| RES    | reserved                                                     |

|--------|--------------------------------------------------------------|

| MXEN   | 1- Mouse multiplexing mode enabled by command                |

| M3PEND | 1– Mouse multiplexing mode command pending port 3            |

| M2PEND | 1– Mouse multiplexing mode command pending port 2            |

| M1PEND | 1– Mouse multiplexing mode command pending port 1 (internal) |

| M3DIS  | 1– Direct port 3 clock disable by command                    |

| M2DIS  | 1– Direct port 2 clock disable by command                    |

| M1DIS  | 1– Direct port 1 clock disable by command                    |

|        |                                                              |

#### R16: 8042 configuration register 1 bit definitions (R)

| bit7 | bit 6 | bit 5 | bit 4  | bit 3 | bit 2 | bit 1 | bit 0  |

|------|-------|-------|--------|-------|-------|-------|--------|

| OK2  | KB2   | 5BUT2 | WHEEL2 | OK3   | KB3   | 5BUT3 | WHEEL3 |

#### R16: 8042 configuration register 1 bit descriptions (R)

| OK2    | 1– External device on port 2 initialized OK |

|--------|---------------------------------------------|

| KB2    | 1– Device on port 2 is a keyboard           |

|        | 0– Device on port 2 is a mouse              |

| 5BUT2  | 1- Device on port 2 is a 5-button mouse     |

| WHEEL2 | 1- Device on port 2 is a wheel mouse        |

| OK3    | 1- External device on port 3 initialized OK |

| KB3    | 1– Device on port 3 is a keyboard           |

|        | 0- Device on port 3 is a mouse              |

| 5BUT3  | 1- Device on port 3 is a 5-button mouse     |

| WHEEL3 | 1- Device on port 3 is a wheel mouse        |

|        |                                             |

#### **R17: 8042 configuration register 2 bit definitions (R)**

| bit7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0  |

|------|-------|-------|-------|-------|-------|-------|--------|

| RES  | RES   | RES   | RES   | RES   | OK1   | 5BUT1 | WHEEL1 |

#### R17: 8042 configuration register 2 bit descriptions (R)

| RES<br>OK1 | reserved<br>1- Internal device on port 1 initialized OK |

|------------|---------------------------------------------------------|

| 5BUT1      | 1– Device on port 3 is a 5-button mouse                 |

| WHEEL1     | 1- Device on port 3 is a wheel mouse                    |

ACPITroller™ Basic UR8HC342 **Preliminary** system management controller product

This page intentionally left blank

AlphaKey<sup>™</sup> keyboard manager

## USAR UR8HC342 ACPITroller™ AlphaKey™ keyboard manager

### Overview

The USAR AlphaKey<sup>™</sup> keyboard manager is the most advanced keyboard management module in the industry today and the first one to integrate the laptop keyboard matrix with system management tasks through ACPI and SMBus.

The USAR AlphaKey<sup>™</sup> keyboard manager provides OEMs with extreme flexibility both with PS/2 keyboard functionality, as well as with user control, from the keyboard, of system management tasks through ACPI and SMBus.

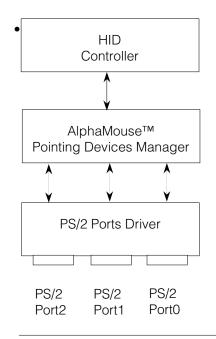

The USAR AlphaKey<sup>™</sup> keyboard manager, as shown in the following diagram, communicates with the HID controller, the ACPI embedded controller, the virtual SMBus device manager and the external PS/2 ports of the USAR ACPITroller<sup>™</sup>.

#### AlphaKey<sup>™</sup> communications block diagram

The USAR AlphaKey<sup>™</sup> keyboard manager can simultaneously support both an external keyboard (including Windows<sup>®</sup> and Japanese layout keyboards)

and an internal scanned key matrix. The internal scan matrix layout can be programmed through an extended set of keyboard commands. The USAR

AlphaKey<sup>™</sup> keyboard manager handles PS/2 keyboard commands, supports external keyboard hot-plug-ins, and merges internal and external keyboard data as if they were coming from one source.

## USAR AlphaKey<sup>™</sup> features at a glance

- Supports IBM standard 101/102 keyboards including Windows<sup>®</sup>, On-Now Power keys, Japanese keyboard keys, and Korean keyboard keys.

- External keyboard and internal keyboard operate simultaneously; data is merged

- User can hot-plug external keyboard

- Auto-detection of type of device in any external PS/2 port

- N-key rollover and ghost key detection

- Programmable scan matrix

- Embedded numeric keypad support

- Supports all three scan code sets

- Interoperability between 3-volt systems and 5-volt PS/2 devices without any external level-shifting circuitry

- Unique "Zero-Power™" operation of the scanned matrix AND the PS/2 embedded port

- "Protocol safe" handling of external PS/2 devices

AlphaKey™ keyboard manager

## USAR AlphaKey<sup>™</sup> hardware configuration

The USAR AlphaKey<sup>™</sup> keyboard manager interfaces directly to the signals of the scanned matrix, the external PS/2 ports and the LEDs' port. This section describes the handling of the signal lines and the options OEMs have in configuring the hardware interfaces of the USAR AlphaKey<sup>™</sup> keyboard manager.

#### **Scanned matrix**

The USAR AlphaKey<sup>™</sup> embedded keyboard is organized as an 8 x 16 matrix. While the maximum matrix size and the organization of rows and columns are fixed, smaller matrixes can be accommodated. The USAR AlphaKey<sup>™</sup> matrix comes configured with a default key layout described in Appendix B of this document.

OEMs requiring a custom matrix layout are presented with the option to either order the ACPITroller<sup>™</sup> delivered with their own matrix specification or use the programming facilities of the USAR ACPITroller<sup>™</sup>. Configuration of the matrix layout can be accomplished though the USAR Extended Command set of the HID controller (8042), and it is described in detail later in this section. Custom configuration information is stored in the AlphaKey<sup>™</sup> RAM and has to be downloaded into the controller each time power is recycled. Alternatively, information can be stored permanently in the controller's flash RAM area – if available – or in a EEPROM residing in one of the SMBus ports of the controller. AlphaKey<sup>™</sup> keyboard manager

#### LED port

The USAR AlphaKey<sup>™</sup> keyboard manager supports up to four LEDs. Three LEDs correspond to the standard 101/102 PS/2 keyboard Numeric Lock, Caps Lock and Scroll Lock LEDs. The fourth LED is the Katakana LED used in Japanese keyboards. OEMs have the option either to utilize the LEDs or to disable them in order to use the LED port for other general input/output functions. The configuration of the LED port is in the AlphaKey<sup>™</sup> control register, and it is described later in this section.

#### **External PS/2 ports**

The USAR AlphaKey<sup>™</sup> supports three PS/2 ports, all of them functioning with USAR's patented "Zero-Power<sup>™</sup>" operation. Each of the three PS/2 ports is available for either a PS/2 keyboard or a PS/2 mouse-type device. The USAR AlphaKey<sup>™</sup> keyboard manager detects the hot-plug-in of an external keyboard, and integrates its data input with the input from the embedded keyboard matrix. The USAR AlphaKey<sup>™</sup> responds to and implements every PS/2 keyboard command, and individually handles communications with externally connected keyboard devices.

In addition to this mode, the USAR AlphaKey<sup>™</sup> can support a pure 8042 type of operation, in which the externally connected keyboard provides the responses to the system-issued PS/2 commands. This mode is implemented in order to support proprietary devices that identify themselves as PS/2 keyboards; however, they require special drivers in order to operate properly. Setting the KLHDIS bit of the control register to one (1) activates the pure 8042 mode. While in this mode, only the first connected external PS/2 keyboard is enabled, in order to avoid conflicting responses from other devices to the custom driver.

#### Auto-detection of device type in external PS/2 ports

The USAR ACPITroller<sup>™</sup> auto-detects the type of PS/2 device connected to either one of the two external PS/2 ports and configures the device properly according to the current system and driver settings. Users can connect any type of PS/2 device (keyboard or mouse) to either port. Data from any keyboard(s) detected are routed to the USAR AlphaKey<sup>™</sup> keyboard manager for proper initialization and data handling.

#### 3-volt and 5-volt operation of PS/2 ports

The USAR ACPITroller<sup>™</sup> can be powered by either a 3-volt or a 5-volt power supply. Even when powered by a 3-volt power supply, the USAR ACPITroller<sup>™</sup> communicates flawlessly with 5-volt powered PS/2 devices, without any additional level-shifting circuit.

AlphaKey<sup>™</sup> keyboard manager

# PS/2 keyboard protocol command and data handling

The USAR AlphaKey<sup>™</sup> fully implements the PS/2 keyboard command protocol including support for scan code set 3 specific commands. Support of scan code set 3 provides compatibility with all operating systems ported to the Intel x86 architecture. The USAR AlphaKey<sup>™</sup> keyboard manager, which responds to and executes all PS/2 keyboard.

The table below lists the PS/2 commands supported by AlphaKey<sup>™</sup> as well as the corresponding responses to them.

| Command      | Response        | Description                          |  |  |

|--------------|-----------------|--------------------------------------|--|--|

| FFh          | Fah, AAh        | Keyboard reset command               |  |  |

| FEh          | XXh             | Resend last byte transmitted         |  |  |

| FDh, XXh     | Fah, FAh        | Set key make (key)                   |  |  |

| FCh, XXh     | Fah, FAh        | Set key make/break (key)             |  |  |

| FBh, XXh     | Fah, FAh        | Set key typematic (key)              |  |  |

| FAh          | Fah             | Set all keys typematic/make/break    |  |  |

| F9h          | Fah             | Set all keys make                    |  |  |

| F8h          | Fah             | Set all keys make/break              |  |  |

| F7h          | Fah             | Set all keys typematic               |  |  |

| F6h          | Fah             | Set default                          |  |  |

| F5h          | Fah             | Disable                              |  |  |

| F4h          | Fah             | Enable                               |  |  |

| F3h , XXh    | Fah, FAh        | Set typematic delay and rate (value) |  |  |

| F2h          | Fah, 8Xh, ABh   | Read device ID                       |  |  |

| F1h          | Feh             | Invalid command                      |  |  |

| F0h, 00 – 03 | Fah, FAh, (0Xh) | Set scan set (value)                 |  |  |

|              |                 | 0 = Programmable keyboard matrix     |  |  |

| EFh          | Feh             | Invalid command                      |  |  |

| EEh          | Eeh             | Echo                                 |  |  |

| EDh, 0Xh     | Fah, FAh        | Set LEDs (value)                     |  |  |

#### **PS/2 command & response codes**

#### Protocol Safe™ handling of external PS/2 keyboards

The USAR AlphaKey<sup>™</sup> keyboard manager provides a level of protocol isolation between the external PS/2 keyboard(s) and the host system. Even when an external keyboard is connected, commands issued by the system are responded to and executed internally within the USAR AlphaKey<sup>™</sup> keyboard manager. The USAR AlphaKey<sup>™</sup> keyboard manager subsequently relays only relevant commands to the external device(s) and it processes locally any hand-shaking, including errors and recovery messages.

This unique mode of operation provides the system with two benefits:

- It isolates the system from bad implementations of the PS/2 keyboard protocol from external keyboards. The USAR AlphaKey<sup>™</sup> directs to the external keyboard only the simplest commands required for data entry and LED handling and it handles internally the more complicated commands. It basically uses the external device the same way it handles the scanned matrix for pure key entry and it takes full responsibility of the protocol implementation. The system "sees" a consistent PS/2 keyboard protocol implementation independently of the PS/2 keyboard the user has connected to the external PS/2 ports.

- It improves the system performance. Unlike keyboard controller implementations that rely on the external device to provide command responses, the USAR AlphaKey<sup>™</sup> communicates quickly and efficiently through the X-bus, and hides from the system the overhead of low level PS/2 error handling.

#### USAR AlphaKey<sup>™</sup> Scan Code support

USAR's AlphaKey<sup>™</sup> supports the IBM Standard Scan Code Sets 1, 2, and 3 for all keys, including Windows<sup>®</sup> and the On-Now Power keys (Scan Code 1 & 2 only).

ACPITroller™ Basic UR8HC342 **Preliminary** system management controller product

### USAR AlphaKey<sup>™</sup> keyboard matrix

The USAR AlphaKey<sup>™</sup> implements three distinct key layouts over the same keyboard matrix. Each keyboard matrix layout can be viewed as a separate keyboard selected and activated by the user through the Fn and Num Lock key. The default layout is QWERTY; this is the most commonly used layout, and it includes all keys needed for regular data entry. The NumPad layout can be invoked by setting the Num Lock LED on, and it implements a numeric keypad over part of the matrix for fast numeric entry. The Fn layout is invoked when the user presses the Fn key of the laptop keyboard, and it is used to activate special keys for system functions and custom data functions. The USAR AlphaKey<sup>™</sup> is preprogrammed with a typical laptop keyboard matrix, implementing all three layouts. The preprogrammed matrix and layouts are described in Appendix B of this document.

#### **Keyboard matrix layouts**

The USAR AlphaKey<sup>™</sup> keyboard manager maintains the keyboard matrix layout information in the controller's Matrix RAM area which is described later in this chapter. After a power-on reset, the USAR AlphaKey<sup>™</sup> defaults to Scan Set 1. Subsequently, the OEM can download a custom matrix and/or custom key definitions and assignments through BIOS, TSR programs or device driver software, and select Scan Set 0 to enable the custom matrix.

The following table describes the matrix layouts supported by the USAR AlphaKey™.

| Fn   | Num  |               |

|------|------|---------------|

| Key  | Lock | Description   |

| Up   | Off  | QWERTY layout |

| Up   | On   | NumPad layout |

| Down | X    | Fn layout     |

#### USAR AlphaKey™ matrix layouts

### USAR AlphaKey<sup>™</sup> key numbers

The action invoked by a key press is determined primarily by the USAR key number assigned to the specific matrix location.

Each matrix location has a USAR key number assigned to it. If a matrix location is empty (no physical switch), or if the switch should produce no action in specific layouts, the null key number can be assigned into the specific position.

USAR has defined four distinct ranges of key numbers. The following table describes the USAR defined key number ranges for keys supported by the AlphaKey<sup>™</sup> keyboard manager.

#### USAR AlphaKey<sup>™</sup> key number ranges

| Key numbers (hex) | No of keys | Category                                      |

|-------------------|------------|-----------------------------------------------|

| 00 - 7F           | 128        | Standard PS/2 keys                            |

| 80 - AF           | 48         | Alternate layout keys (NumPad and Fn layouts) |

A description of the codes in each of these ranges follows.

#### Standard PS/2 keys

USAR AlphaKey<sup>™</sup> uses 128 unique numbers 00-7Fh (0-127) to describe the Standard PS/2 keys implemented in most standard PS/2 keyboard layouts. The key numbers for Standard PS/2 keys are fixed and they are re-used. Note the following special key ranges:

| 0         | Null key                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------|

| 1 - 101   | 101/102 Keyboard keys                                                                                                          |

| 102 – 104 | Windows keys.                                                                                                                  |

| 105       | Overrun error                                                                                                                  |

| 106       | Function (Fn) key                                                                                                              |

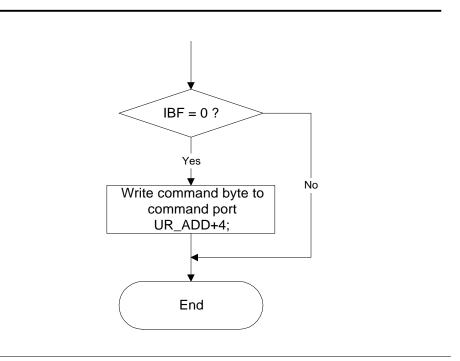

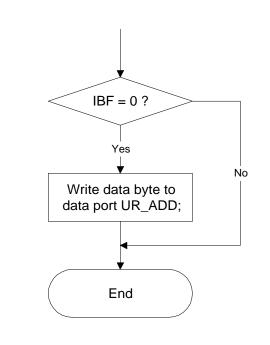

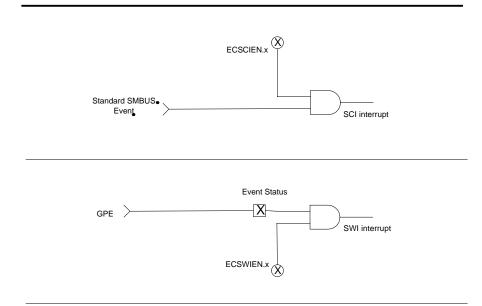

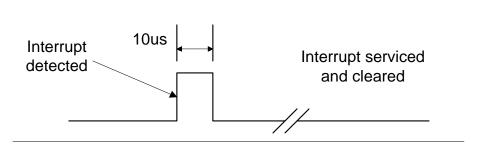

| 107       | Sticky mode key. This key is used to toggle the "sticky" mode of operation of the PS/2 shift keys (Ctrl, Shift, Alt, Win Keys) |